5나노 트랜지스터 시대 개막…IBM·삼성·GF 공정개발

송고시간2017-06-05 13:01

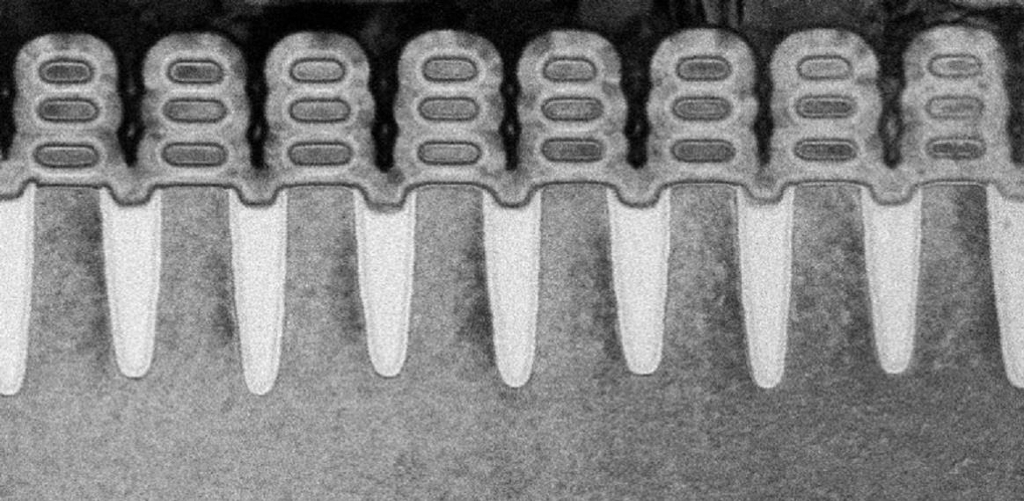

(서울=연합뉴스) 임화섭 채새롬 기자 = IBM·삼성·글로벌파운드리(GF)가 참여하는 IBM 리서치 연합은 업계 최초로 5나노미터(nm) 칩 제조가 가능한 실리콘 나노시트 트랜지스터 생산 공정 개발에 성공했다고 5일 밝혔다.

이는 IBM이 2015년 7월 공개한 7nm 공정의 후속 기술이며, 작년에 상용화된 현행 10nm 공정보다 두 세대 앞선 '차차세대' 기술이다.

7nm 공정으로는 손톱만한 크기에 200억 개의 트랜지스터를 집적할 수 있었으나, 이번에 개발된 5nm 공정으로는 같은 크기에 300억 개의 트랜지스터를 넣을 수 있다.

10nm 칩과 비교하면 동일한 전력 소모 시 성능이 40% 향상되고, 동일한 성능에서는 전력 소모량이 75% 감소할 것이라고 IBM은 설명했다.

이에 따라 전력 효율이 개선되면서 스마트폰 등 모바일 기기의 배터리 지속 시간이 지금의 최대 2∼3배로 늘어날 수 있게 된다.

또 전력 소모가 적고 성능이 높은 칩이 보급되면 클라우드를 통해 제공되는 인공지능(AI) 등 인지 컴퓨팅(cognitive computing)과 사물인터넷(IoT) 등 데이터 집약적 애플리케이션의 성능 향상과 관련 기술 발전 가속화가 기대된다고 IBM은 설명했다.

IBM은 5nm 칩을 머지 않은 미래에 생산할 수 있을 것으로 보고 있다. 다만 구체적 상용화 일정은 발표하지 않았다. 7nm 생산 공정은 대만 TMSC가 올해 말이나 내년 초에 이를 이용한 초도 생산에 착수할 가능성이 있는 것으로 알려졌다.

이번 공정 개발은 IBM이 2014년에 발표한 반도체 투자 계획에 따른 것이다. IBM은 당시 향후 5년간 30억 달러(3조4천억 원)를 반도체 분야에 투자하겠다고 밝혔다.

개발팀은 기존의 핀펫(FinFET) 아키텍처 대신 실리콘 나노시트 스택(여러 개의 나노층을 쌓은 것)을 사용한 트랜지스터 디바이스 구조를 만들었다. 핀펫 구조는 기존 평면(2D) 구조의 한계를 극복하기 위해 도입된 입체(3D) 구조의 공정 기술로, 구조가 물고기 지느러미(fin)와 비슷해 이런 이름이 붙었다.

solatido@yna.co.kr, srchae@yna.co.kr

제보는 카카오톡 okjebo <저작권자(c) 연합뉴스, 무단 전재-재배포, AI 학습 및 활용 금지> 2017/06/05 13:01 송고

![[영상] 이란 핵시설지역서 '쾅' 폭발음…이스라엘, 이란 본토 보복 타격](http://img2.yna.co.kr/mpic/YH/2024/04/19/MYH20240419015300704_P4.jpg)

![[영상] 무개념 행동 다 찍혔다…새끼곰 억지로 끌어내려 '인증샷' 찰칵!](http://img6.yna.co.kr/mpic/YH/2024/04/19/MYH20240419014600704_P4.jpg)

![[영상] 한미 특전사 공중침투훈련 성료…사상자 발생한 북한과 대비](http://img9.yna.co.kr/mpic/YH/2024/04/19/MYH20240419013800704_P4.jpg)